### Research topics:

- ▶ Silicon photonics systems

- Next generation data

- High speed configurable logic

Computing solutions for high performance data filtering

#### ICE-DIP 2013-2017: The Intel-CERN European Doctorate Industrial Program

>>> A public-private partnership to research solutions for next generation data acquisition networks, offering research training to five Early Stage Researchers in ICT

# The points of my research Data Transfer

- Move data <u>fast</u> to manycore processors

- Develop <u>easy to use</u> intra/inter-machine communication interface

- Study the <u>trade-offs</u> of related communication patterns and mechanisms

- Conduct this research in the context of next generation DAQs

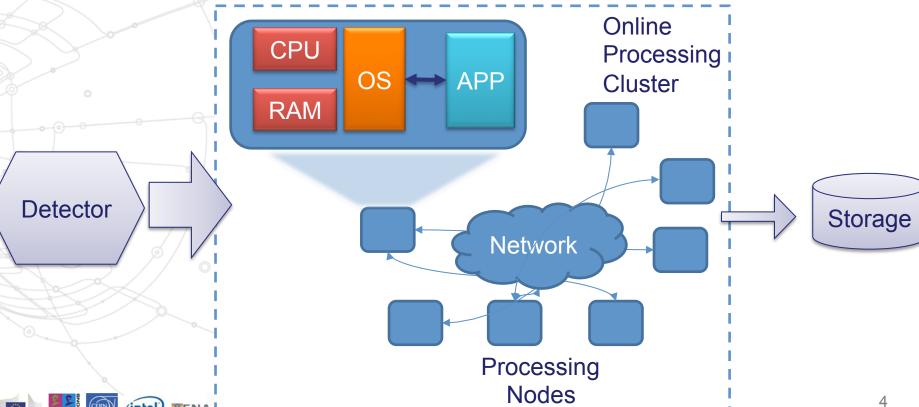

## Distributed application for online processing

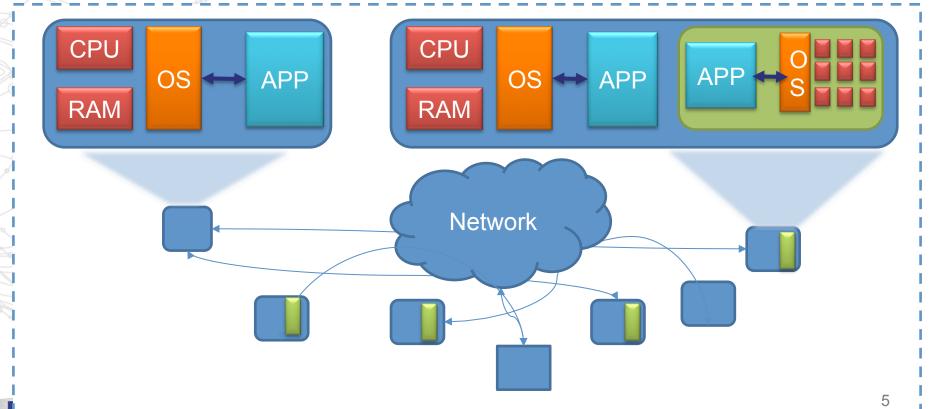

# Heterogeneous computing with manycore co-processors

## We need high efficient transport

IMC (intra-machine) **CPU CPU** OS  $\iff$  APP **APP** RAM **RAM RDMA** Network A server executing part A server equipped with a of the O<sup>2</sup> distributed manycore co-processor processing system. executing "accelerated" apps.

Online-Offline system for ALICE

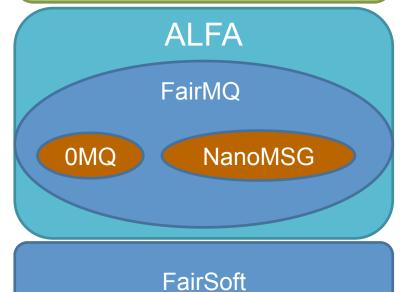

Software framework for ALICE and Fair experiments

External Dependencies

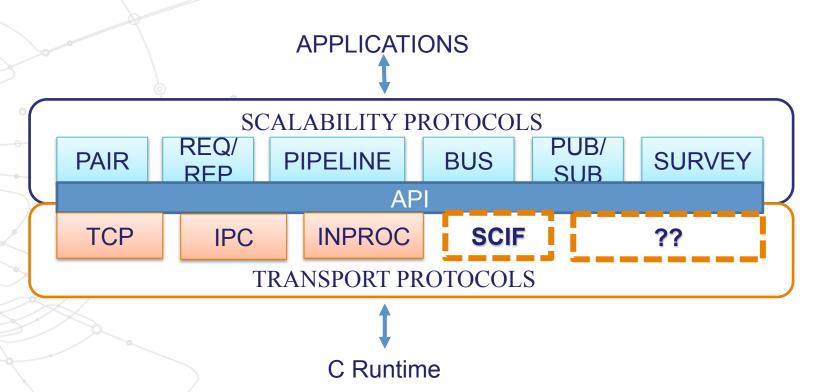

# **Boosted NanoMSG's performance of Intra-machine communication**

NN PIPELINE (Push/Pull) Co-Processor **INPROC IPC** TCP (400MB/s) SCIF(5.7 GB/s) **PCIe** Host

### NanoMSG extended with SCIF support

## **Future plans**

- Focus more on ZeroMQ

- Develop a <u>message-passing to RDMA</u> mapping protocol

- Study ALFA and O<sup>2</sup>

- > Experiment on <u>infiniband</u> hardware

- Work on getting early access on KNL and OmniPath.